PCB subsystem architecture design

Zuken’s CR-8000 is the most advanced PCB design platform in the industry with architecture design and verification, multi-board PCB layout with MCAD integration, SI/PI analysis, and chip/package/board co-design. CR-8000 is for your most challenging PCB subsystem designs.

What CR-8000 can do for you

PCB subsystem architecture design

Partition complex systems into multiple connected PCBs

Manage IC, package and PCB in one single environment

Control releases, revisions and configurations with integrated data management

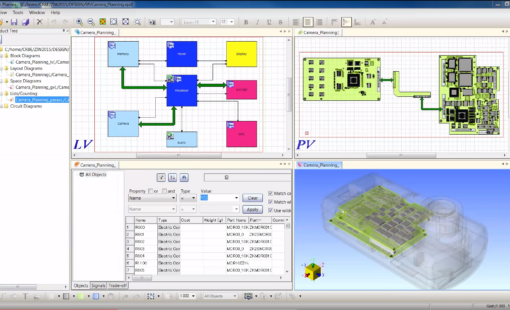

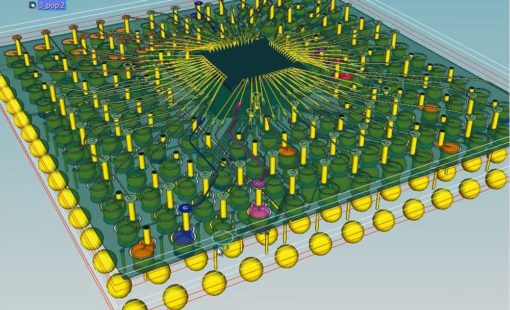

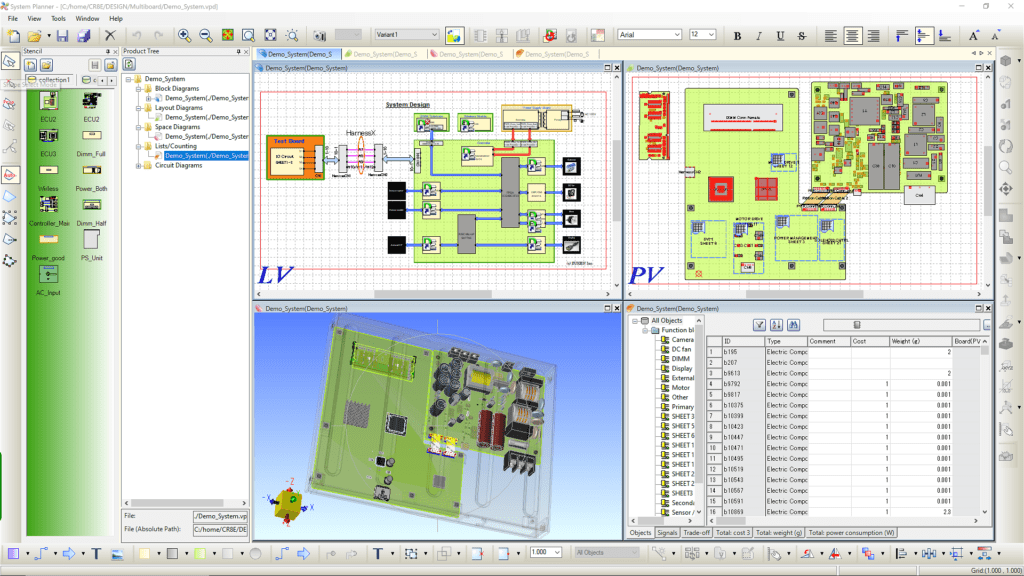

System Planner is the industry’s only hardware architecture design and verification tool that is fully integrated with detailed PCB and wire harness design. As products become more complex, optimizing the architecture is more critical than ever.

System Planner combines four disciplines into one design and analysis experience. Design multi-board systems with imported MCAD enclosures. Floor plan your design across multiple boards for optimal routing and connectivity. Verify cost and weight targets with parametric analysis. Move your design seamlessly to a detailed design.

System PlannerArtificial Intelligence (AI) is an evolving and promising tool in the field of PCB design. Additionally, whether you’re a design veteran or a newcomer, AI offers many benefits that can make your life easier. However, it’s not without its challenges. As technology progresses, the only question is: Are you ready for the AI-driven future of PCB design?

AI PCB Design

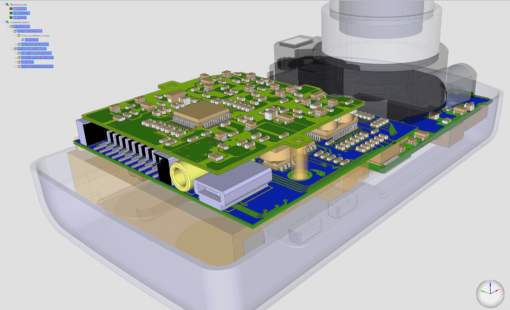

As product complexity grows, PCB design must be considered in the context of the subsystem. A PCB subsystem design platform includes support multi-board design and analysis, MCAD integration, and wire harness design. CR-8000 goes beyond the subsystem to include chip/package/board co-design.

As companies move to Digital Engineering and model-based design processes, the need for a subsystem design solution is critical. Detailed design teams will be handed a subsystem for implementation, not a PCB. CR-8000 is built for subsystem implementation.

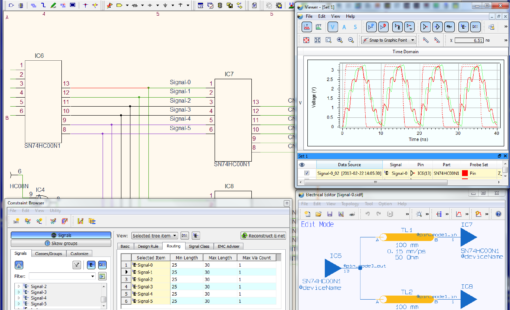

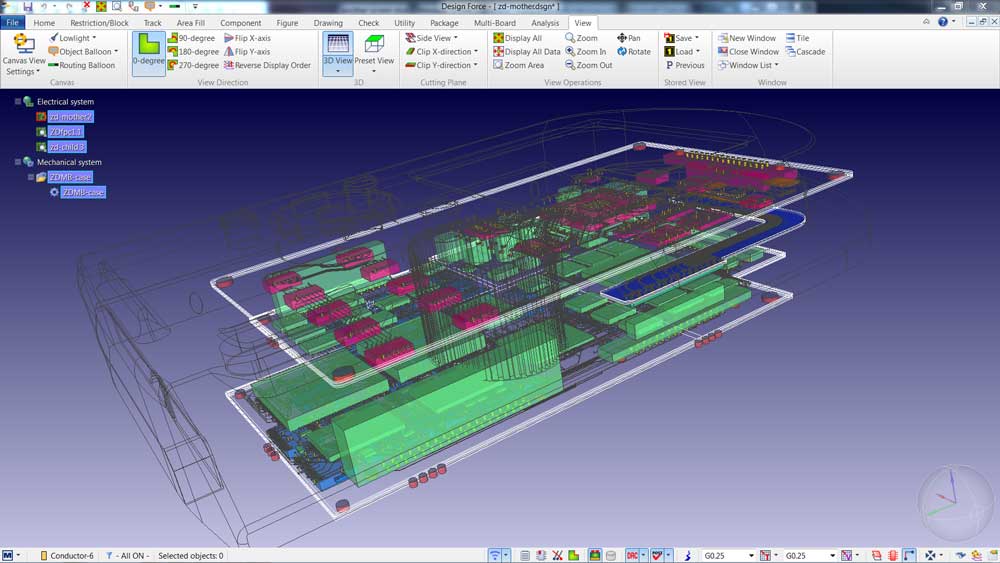

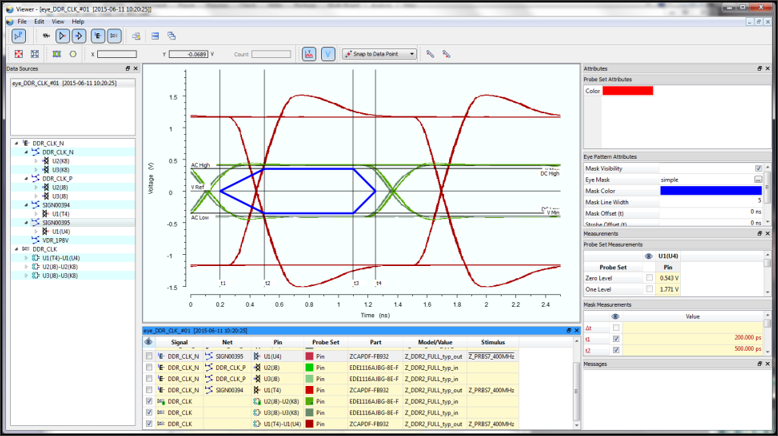

Design ForceToday’s complex boards or multi-board systems require detailed planning and analysis. CR-8000 provides you with all the tools to build high fidelity boards with integrated signal and power integrity analysis with pre-layout planning. Full board EMI analysis for fast and efficient EMI screening.

Third-party integrations with Ansys and Keysight bring additional capabilities from the industry leaders.

Analysis

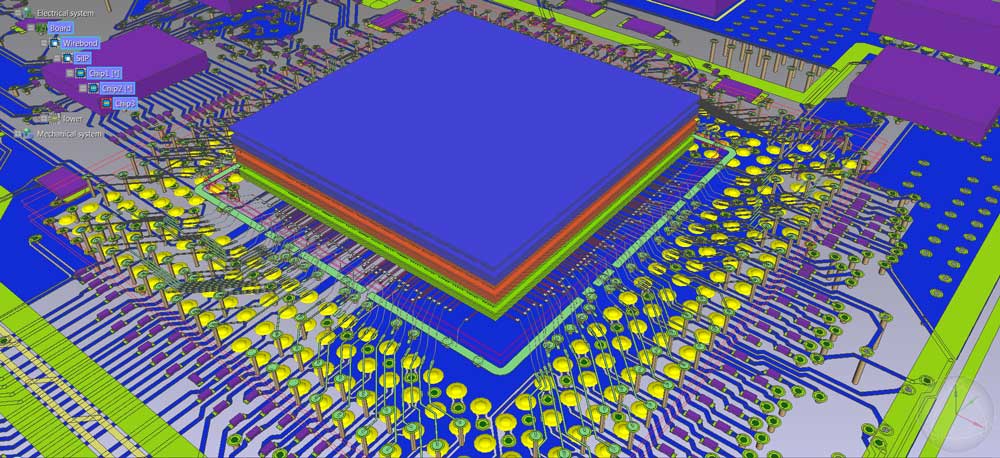

Design Force offers an intuitive, integrated environment for designing single and multi-die packages for wire-bond, flip-chip, and high-density advanced packaging. Designers can start designs with early prototype input of chip and package data from the library, reuse data from IC layout tools, and take advantage of parametric wizards to streamline the creation of the system.

IC PackagingPLM systems are excellent at managing manufacturing data. But companies need to manage component libraries and work-in-process data on a day-to-day basis prior to release for manufacturing. Zuken’s DS-CR provides WIP design data management, design collaboration, project management, design re-use, “where-used” traceability, and much more.

DS-CR is also fully integrated with leading PLM systems for the manufacturing hand-off or component information synchronization. Component information can be automatically synchronized with supply chain partners.

DS-CR

DFM Center enables designers to handle the increasing complexity and diversity of today’s PCBs while ensuring high final product quality, and accurate outputs for the manufacturing processes. With a robust set of features for data preparation and embedded verification to ensure manufacturing specifications are met, DFM Center addresses the challenges of the manufacturing process.

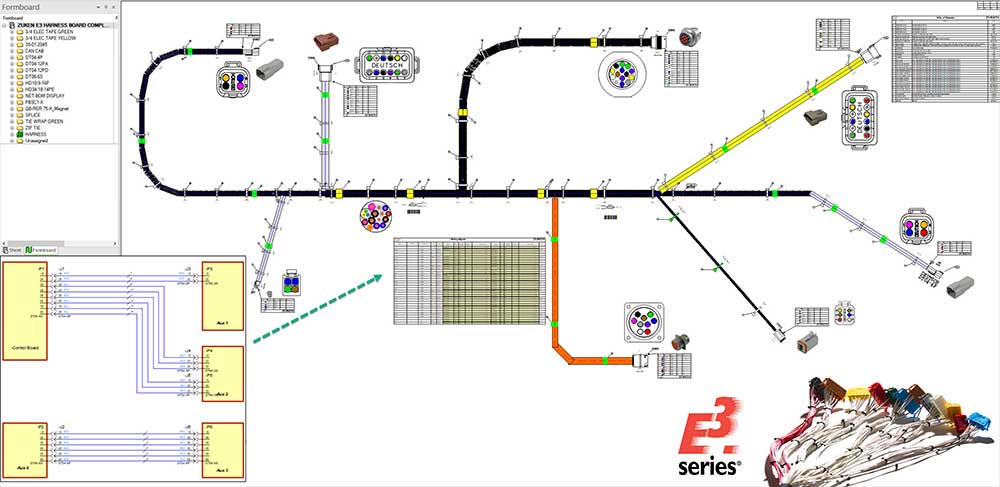

DFM CenterAs products get more complicated, the siloed approach to detailed design is missing the mark. Wire harness pin assignments are commonly out of sync with the PCB. A subsystem design approach including PCB, wire harness, and MCAD eliminates those common errors.

Many companies complete the PCB prior to the harness design. Zuken has embraced this approach by using a standard PCB manufacturing output, IPC-2581, to design the wire harness. Zuken’s E3.series imports IPC-2581 directly from CR-8000 eliminating design errors.

E3.series

Check out our latest webinars, white papers, blog posts, tech tips & more

We can help you select the right products

System Planner provides a system-level design environment for the architectural planning and optimization of electronic systems and products. It enables engineers to optimize partitioning and performance of multi-board systems and maximize design reuse, while eliminating the need to re-enter up-front planning data into the design tools during detailed design.

PCB Design Creation - Design Gateway is a platform for logical circuit design and verification of single and multi-board system-level electronic designs. It supports a true system-level circuit design in which individual circuits can be represented and connected as blocks.

Design Force combines traditional 2D design with native 3D design and the latest human interface techniques, accelerated graphics and almost instantaneous rendering and refreshing. It is the fastest, most effective PCB design solution available today. Design Force enables design teams to layout their designs in the context of a complete system or product.

Design Force offers an intuitive, integrated environment for designing single and multi-die packages for wire-bond, flip-chip, and high density advanced packaging. Designers can start designs with early prototype input of chip and package data from the library, reuse data from IC layout tools, and take advantage of parametric wizards to streamline the creation of the system

PCB Design for Manufacturing (DFM) enables designers to handle the increasing complexity and diversity of today’s PCBs, while ensuring high final product quality, and accurate outputs for the manufacturing processes. With a robust set of features for data preparation and embedded verification to ensure manufacturing specifications are met...

Zuken’s engineering data management platform DS-CR has been created to support the specific demands of PCB design data management. It combines multi-site library, design data and configuration management into a unified engineering environment.